ソフトウエアによるデジタル回路開発の取り組み

2021.07.05

1.はじめに

当社は国内有数のマイクロ波技術のエキスパート企業を自負しておりますが、一方、近年は時代の流れに乗ってデジタル技術にも注力しはじめています。今回は当社にてデジタル系の装置開発における生産性と保守性の改善や人手不足解消などを目的として準備を進めている「ソフトウエアによるデジタル回路開発(高位合成)の取り組み」について簡単な実例を題材に紹介させて頂きます。

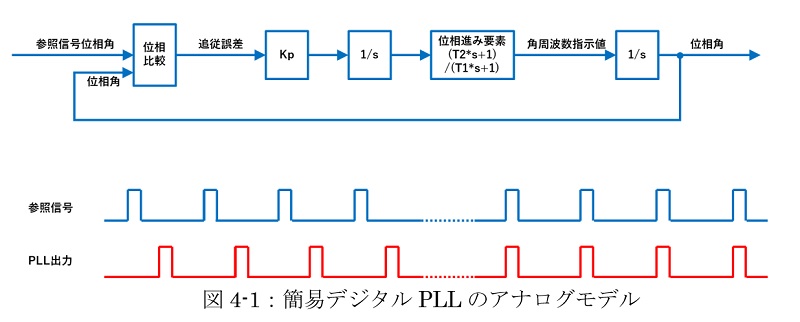

2.簡易デジタルPLL

題材としてはデジタルPLLを取り上げます。デジタルPLLはその回路自体はごくごく簡単なものですが事前のシミュレーション確認が非常にやりにくいなど実装は敬遠されがちなものでした。これをソフトウエアによるデジタル回路開発に切り替えることで誰もが素早く容易に実装できることを示します。

3.ソフトウエア開発環境と実装対象

- 制御系設計

- :Octave(フリーの汎用解析ツール)

- ソフト開発

- :GCC(フリーのソフト開発環境)

- シミュレーション

- :GCC(フリーのソフト開発環境)

- 高位合成

- :Vivado-HLS2019.2(2019.2版、フリーの高位合成環境)

- 回路合成

- :Vivado2019.2(Artix-7であればフリーの範囲内で合成可能)

- 実装対象

- :Artix-7 35T(安価なArty-A7基板上のFPGA)

今回は誰もが容易にできることを示すために開発の全てを容易に入手可能なフリーソフトで実施しました。また今回はソフトウエアのみでデジタル回路開発ができることを強調するために開発とシミュレーションは汎用のソフトウエア開発ツールのみで行い、高位合成ツールや回路合成ツールは単なる変換ツールとして用い、それらを使ってのシミュレーションなどは一切行っておりません。

4.仕様と系統図

簡易デジタルPLLの仕様を以下に示します。外部から入力する参照信号はGPSレシーバーの1PPS出力(1 Pulse Per Second)を想定しました。また、目で見てPLLの動きがストレスなく観察できるようにゲイン交差周波数(≒ループ帯域)は高めに設定しています。

(簡易PLL仕様)

- 参照信号

- :約1秒周期のポジティブパルス、デューティ比規定無し。パルス欠損やノイズ等による疑似パルス発生有り。

- 数100秒で数%程度の周期変動有り。

- ゲイン交差周波数

- :ωc=2π×1/30Hz ⇒ ループ帯域に相当(少し高めにしています)

- 追従分解能

- :時間は±10ns程度、周波数は±1uHz程度

- 位相余裕

- :50°以上

- 制御周期

- :1秒(パルスとは独立動作)

以上の仕様からPLLは2型となり、制御器には積分器が1つ必要になります。またデジタルPLLであることからVCOの特性Kvなどは無く、制御対象は単純な積分器(角周波数から位相角を取り出す)となります。後はPLLが2型であることから安定性確保のために制御器には位相補償器が必要となり、今回は位相進み補償器を用います。最後にゲイン交差周波数を調整する比例ゲインKpを準備すれば簡易デジタルPLLの構成要素は全て揃ったことになります。以上を元にした簡易デジタルPLLのアナログモデルの系統図は以下のようになりました。

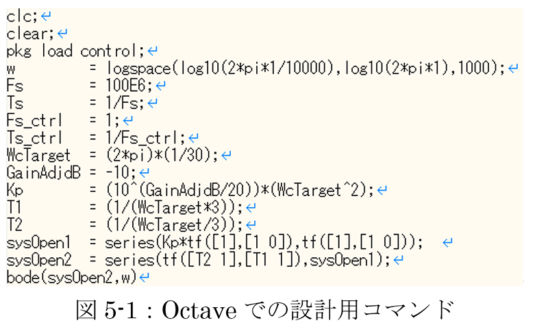

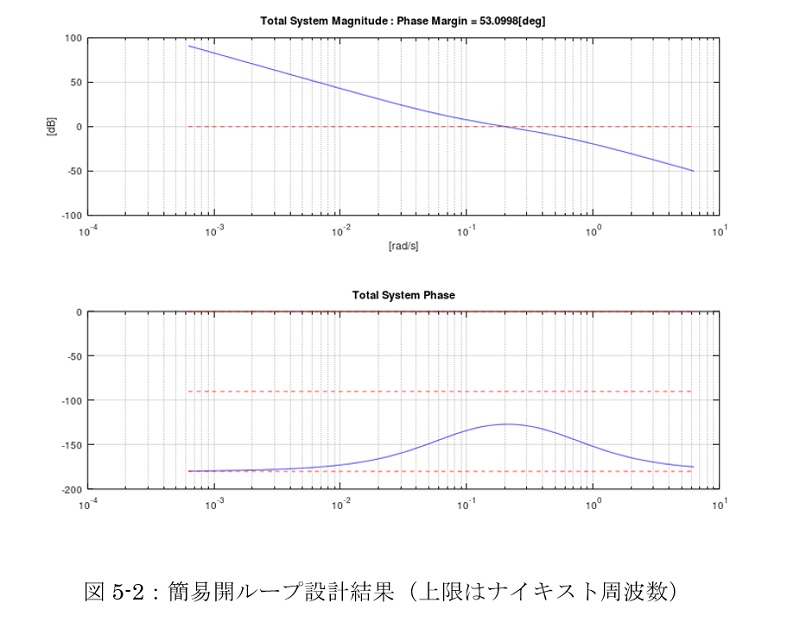

5.簡易ループ設計

上記4のアナログモデルに従って簡易ループ設計した結果を以下に示します。設計は簡単にKpの初期値をT1=T2=0の場合のゲイン交差周波数で決定し、その状態でT1とT2を調整して位相余裕を確保した上でKpの値を微調整してゲイン交差周波数を仕様値に合わせ込んでいます。今回は以下のような結果になりました。

Kp=10^(-10dB/20)×{2π×(1/30Hz)}^2

T1=1/(2π×(1/30Hz)×3)

T2=1/(2π×(1/30Hz)÷3)

この設計はOctaveを使うと以下のわずかなコマンドで設計できます。また最終的に得られたボード線図も示します。

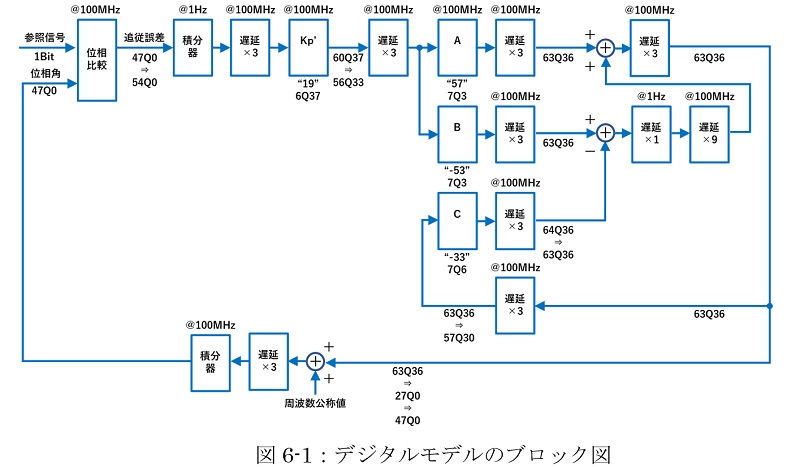

6.デジタル化

設計したアナログモデルのデジタル化を行います。アナログモデルの積分器をデジタルモデルの積分器に変換する際にはサンプリング周期の定数ゲインの追加が必要となります。今回は仕様を満足させるために回路全体を100MHzクロックで動作させ、制御器のみ参照信号の公称周波数に合わせて1Hzで動作させていますが、これらの定数ゲインはKp‘=Kp×1/1Hz×1/100MHzとして1つにまとめました。また制御器の中の位相遅れ要素のデジタル化は例えば双一次変換などを用いて手計算により実現形式を簡単に計算できます。結果は以下のようになります。

- 定数ゲイン

- :Kp‘=Kp×1/1Hz×1/100MHz= 1.3871e-10⇒“+19”@6Q37

- 位相進み要素

- :A+(B-C)×(1/z@1Hz)

- 係数A

- :“+57”@7Q3

- 係数B

- :“-53”@7Q3

- 係数C

- :“-33”@7Q6

以上をブロック図にまとめると以下のようになります。ビット幅などは仕様にある周波数分解能を満たすように、またパラメータの設定誤差が±1%程度になるように決定しました。なお簡易PLLなのでビットスライス時の丸め処理などオミットしておりますのでご了承ください。

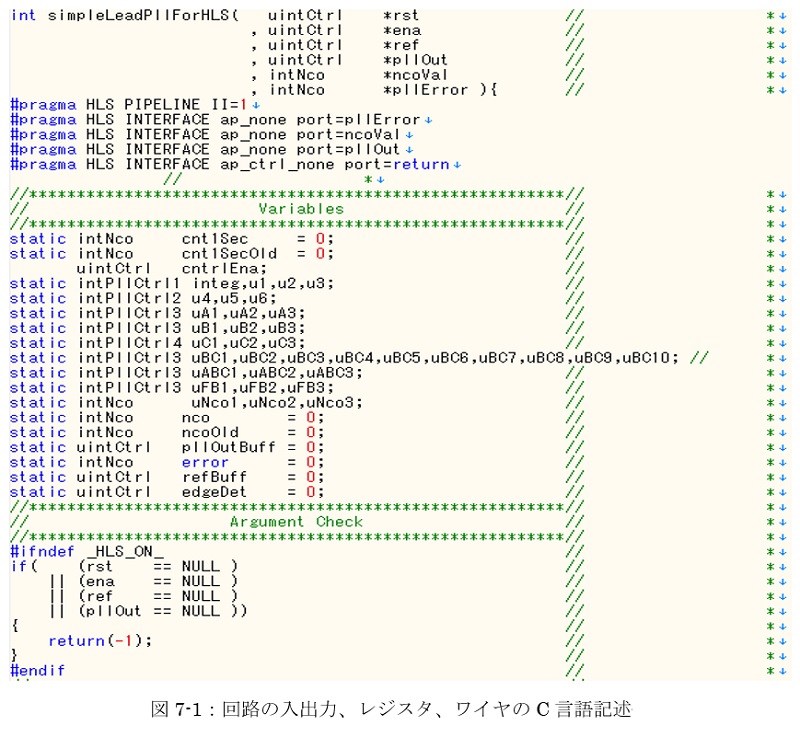

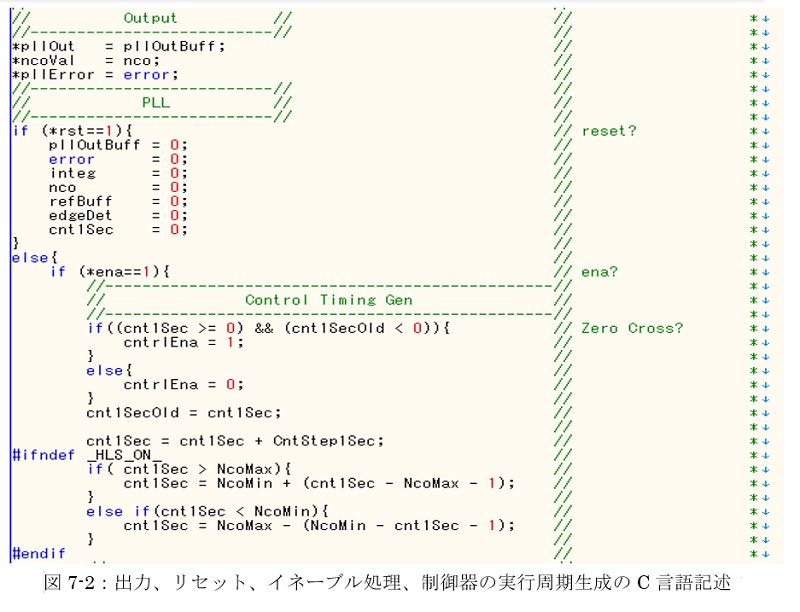

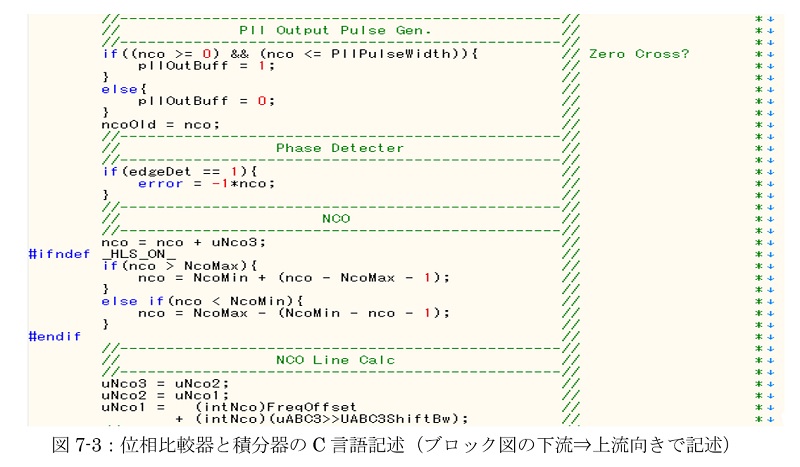

7.簡易デジタルPLLのC言語記述とシミュレーション

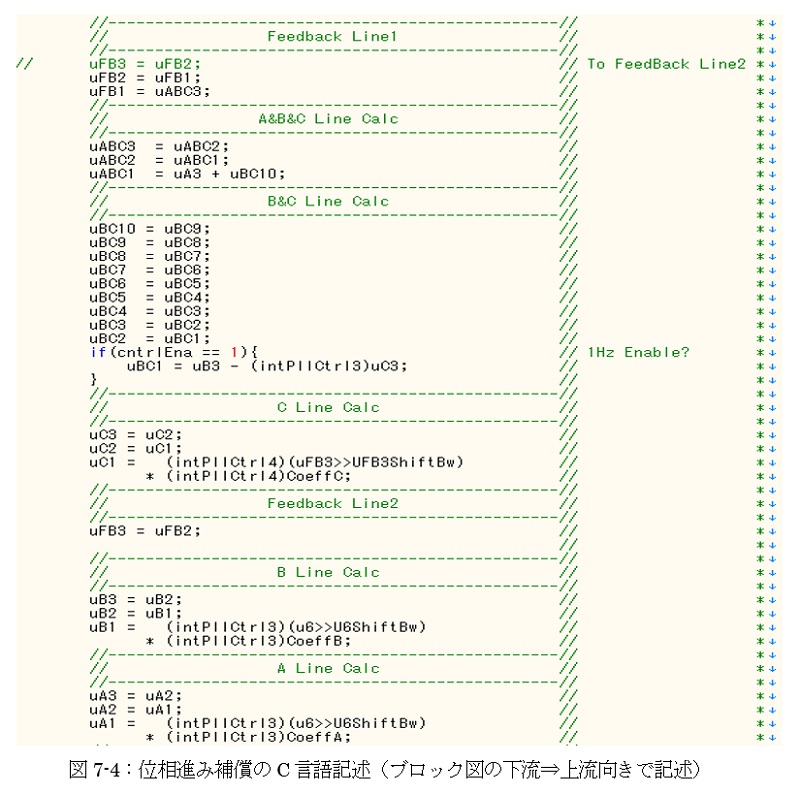

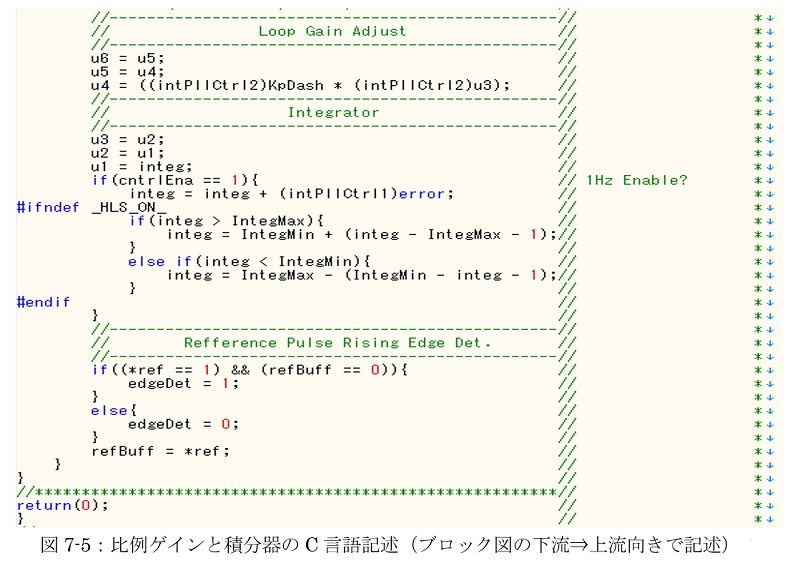

ここからはいよいよソフトウエアによるデジタル回路作成に入ります。先ほどのブロック図をそのままソフトウエアに落とし込めば良いのですがPLLなのでHDL化した際に思った通りのタイミングで動作しないと正常動作しません。これを実現するためのキーポイントは、①サンプリング毎に1回呼び出される関数を作る、②その関数で作りたい回路のデジタル回路シミュレータを作る、③おかしな場所に勝手にレジスタを挿入されないように(例えば積分器のループ内など)適切な場所に多めにレジスタを入れておく(例えば積分器のループ外)などとなります。以下に簡易デジタルPLLのコード例を示します。回路との対応がわかり易いようにforループなどは使わず冗長的に記述してあります。

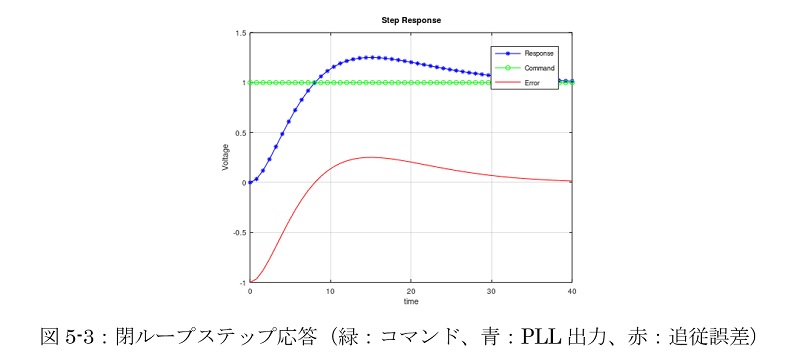

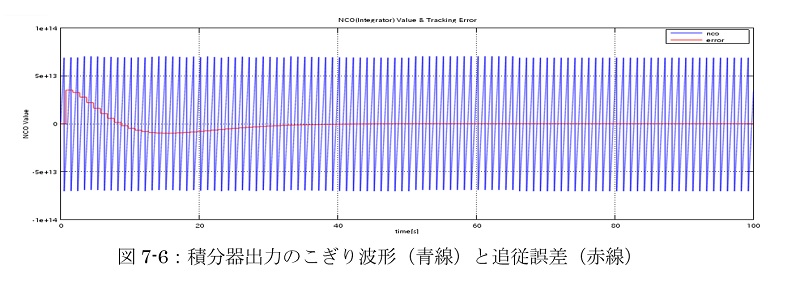

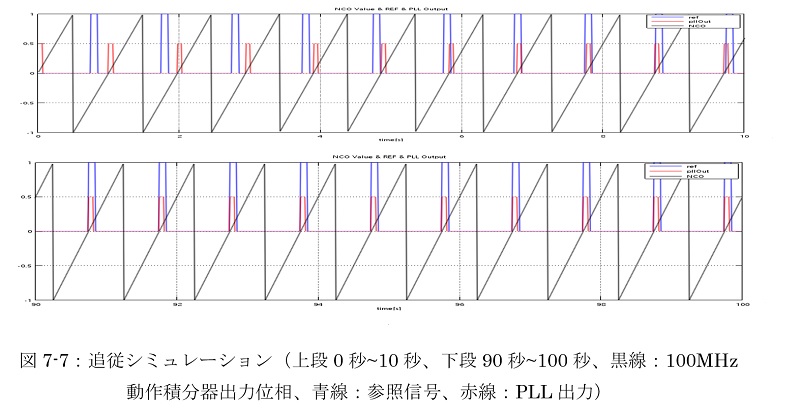

以下にソフトウエア開発ツールによる100MHzサンプリング×100秒=100億サンプリング分のシミュレーション結果を示します(表示は100万分の1に間引き)。追従誤差はアナログモデルのステップ応答シミュレーションとほぼ同じ波形であり40秒程度で参照信号に同期できていることがわかります。通常の高位合成ツールやHDLシミュレーターでこのレベルのシミュレーションをするとかなり時間がかかってしまうと思いますが、ソフトウエアによるシミュレーションだとわずか1~2分で完了でき、ソフトウエアによるデジタル回路開発の威力がわかるかと思います。

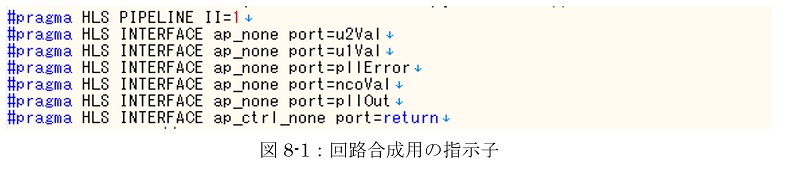

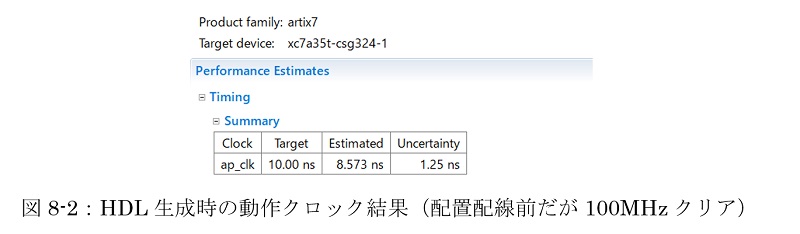

8.高位合成

高位合成は実に簡単で先ほど作成したソースコード一式をそのままVivado-HLSのプロジェクトに放り込んで、回路合成用の指示子を追加して合成ボタンを押すだけです。

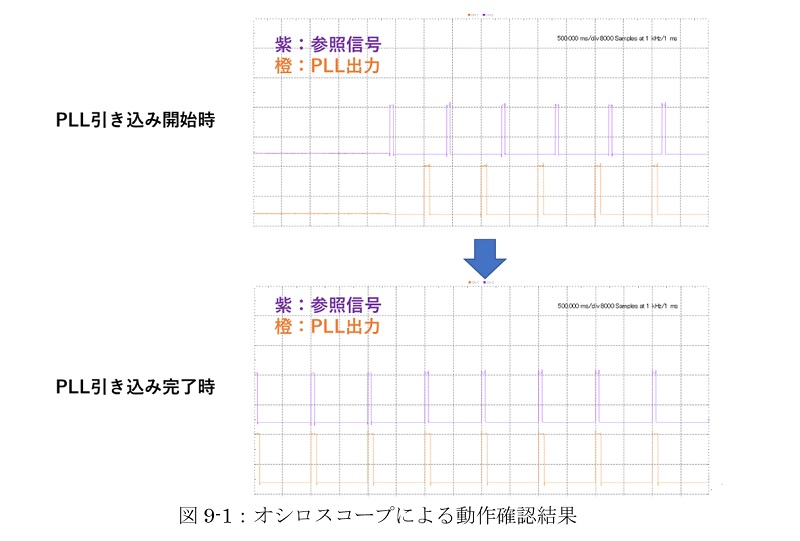

9.簡易PLLの実機動作

生成されたHDLをVivadoにて回路合成し、安価なFPGA評価基板(Arty-A7)に実装して動作させたときの参照信号とPLL出力信号のオシロスコープの画面を以下に示します。紙面では動きが無いのでわかりづらいのですが実際は数十秒かけてPLL出力信号が参照信号に追いついて⇒少し行き過ぎて⇒反対側にほんの少しだけ行き過ぎて、、、を繰り返して外部入力パルス(参照信号)に誤差ゼロで同期していく様子をつぶさに観察することができます。

10.まとめ

国内有数のマイクロ波技術のエキスパート企業を自任する多摩川電子において実施している、ソフトウエアによるデジタル回路開発の取り組みはいかがでしたでしょうか?PLLのようなごく簡単な回路であればあっという間にコーディング、シミュレーション、FPGA実装、実機動作確認が可能でありいろいろと夢が広がります。また機会があれば別の高位合成ツールを用いたこのような取り組みや、全く別の信号処理適用事例などの取り組みを紹介させて頂きたいと思います。

ENGLISH

ENGLISH お問い合わせ

お問い合わせ